# Control of a Three-phase Four-wire Inverter

Liping Zheng and Dong Le Calnetix Technologies LLC Cerritos, CA, USA lzheng@calnetix.com and dle@calnetix.com

*Abstract*— In this paper a three-phase four-leg voltage source inverter operating in island mode is described. The four-leg inverter is implemented by using a delta/wye or ZigZag transformer to meet isolation requirement. The control scheme includes an inner current loop providing the capability of fast current limiting and outer voltage loop. Digital sliding mode control is used for the inner current loop which requires higher bandwidth. The voltage loop is implemented in synchronous frame with selected harmonics cancellation for both positive and negative sequence components. Simulation and test of a 125 kW inverter at various operation conditions are presented to verify the validity of the control method.

*Index Terms*—Three-phase, Island mode, Harmonics cancellation, Current control, Voltage control, Uninterruptible power systems, Pulse width modulation, Inverters, Synchronous frame, Stationary frame.

#### I. INTRODUCTION

There have been increasing demand for ac power supplies or uninterruptible power supplies (UPS) having low voltage distortion. The voltage distortion which is mainly caused by nonlinear and unbalanced loads will lead to load failures and reduced reliability of the inverter. Therefore, some standards specify the harmonics distortion requirement for the inverters. The international Electrotechnical Commission (IEC) 62040-3 recommends that the total harmonics distortion (THD) of sinusoidal output voltages shall be less than 8 % [1]. It also specifies the maximum distortion of the individual harmonics. There are lots of literatures talking about the different control schemes to reduce THD. However, it is still challenging to have low THD at nonlinear and unbalanced condition since in conventional control, the voltage loop bandwidth is too low to compensate for harmonics frequencies.

Because of the high bandwidth requirements of the voltage loop, even some high-performance feedback control schemes, such as deadbeat control [2]-[5], sliding-mode control [6]-[7], can still have high THD at nonlinear and unbalanced load conditions, although they have very good transient performance under large-signal disturbances. To overcome that, other control schemes have been developed, such as internal model based controller [8], optimal control [9], and repetitive control [10]-[11]. Repetitive control has shown promising results in tracking and rejecting periodic signals. Synchronous frame and stationary frame harmonics cancellation are also widely used to reduce THD when in nonlinear load conditions [12]-[15].

In this design, we describe a new control scheme which use digital sliding mode control (DSMC) for the current loop

control in order to have fast current limiting capability which is very crucial when the inverter is running in island mode. The voltage loop is implemented in synchronous frame with selected harmonics cancellation for both positive and negative sequence components. The control scheme is very robust to parameter variation and also is easy to be implemented. A 125kW, 480V inverter has been built to verify the control performance. The simulation and test results show very promising performance.

#### II. TOPOLOGY AND CONTROL SCHEME

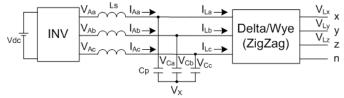

The simplified circuit topology of the developed threephase four-wire island mode inverter is shown in Fig. 1, where  $V_A$  is the inverter stage pulse width modulation (PWM) output voltage,  $I_A$  is the PWM output current,  $I_L$  is the load current in the transformer primary side,  $V_C$  is the voltage in the transformer primary side, and  $V_L$  is the transformer voltage in the secondary side. The isolation transformer which provides three-wire to four-wire conversion can be delta/wye or ZigZag transformer depending on the applications.

Fig. 1. Simplified circuit topology of the inverter in island mode operation.

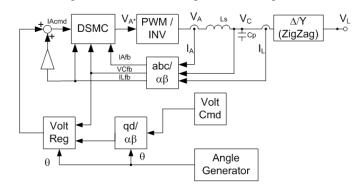

The block diagram of the simplified control scheme is shown in Fig. 2. Due to the large current ripple of the PWM output currents, especially at light load condition, two samples synchronized to each PWM cycle is implemented to reduce the switching harmonics of the sampled current signals.

Fig. 2. Simplified control schematic.

Besides of providing isolation, the Delta/Wye or ZigZag transformer also help to reduce certain order of harmonics. The zero-sequence current is also eliminated in the transformer primary side because of three-wire to four-wire conversion of the transformer. Therefore, after using Clarke's transformation to transform variables from stationary *abc* frame into stationary  $\alpha\beta$  frame using equation 1, only  $\alpha$ -axis and  $\beta$ -axis variables are required to be controlled.

$$[f_{\alpha\beta0}] = [T_{\alpha\beta0}][f_{abc}]$$

<sup>(1)</sup>

where variable f can be currents, voltages, and the transformation matrix is given by

F 4 3 F 7 3 F 4 3

$$T_{\alpha\beta0} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & -\frac{\sqrt{3}}{2} & \frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

(2)

Digital sliding mode control (DSMC) is used for inner current loop control [16]-[17]. By using inner current loop, the inverter can have the capability of fast current limiting. The DSMC current control loop is implemented in stationary  $\alpha\beta$ frame since current loop has much higher bandwidth than voltage loop so higher order harmonics can also be controlled in stationary  $\alpha\beta$  frame. Assuming the load current as disturbances, the current loop subsystem can be written in state space form as

$$\dot{\vec{x}} = A\vec{x} + B\vec{u} + E\vec{d} \tag{3}$$

where the states are

$$\vec{x} = \begin{bmatrix} V_{Cqs} \\ V_{Cds} \\ I_{Pqs} \\ I_{Pqs} \end{bmatrix}, \vec{u} = \begin{bmatrix} V_{Pqs} \\ V_{Pds} \end{bmatrix}, \text{ and } \vec{d} = \begin{bmatrix} I_{Lqs} \\ I_{Lds} \end{bmatrix}$$

(4)

And the coefficients are

0

$$\vec{A} = \begin{bmatrix} 0 & 0 & \frac{1}{C_{p}} & 0 \\ 0 & 0 & 0 & \frac{1}{C_{p}} \\ -\frac{1}{L_{s}} & 0 & 0 & 0 \\ 0 & -\frac{1}{L_{s}} & 0 & 0 \end{bmatrix}$$

(5)

$$B = \begin{bmatrix} 0 & 0 \\ 0 & 0 \\ \frac{1}{L_{s}} & 0 \\ 0 & \frac{1}{L_{s}} \end{bmatrix}$$

(6)

$$E = \begin{bmatrix} -\frac{1}{C_{p}} & 0 \\ 0 & -\frac{1}{L_{s}} \end{bmatrix}$$

(7)

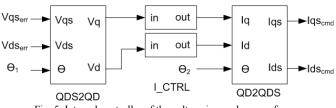

The sliding mode surface of the DSMC is chosen as  $\vec{s}(k) = C\vec{x}(k) - \vec{I}_{cmdqd}(k)$ , and  $C\vec{x}(k) = \vec{I}_{fbqd}(k)$ . The equivalent control input of the sliding mode control can then be derived as [16]:

$$\vec{u}_{eq}(k) = (CB^*)^{-1} (I_{cmdqd}(k) - CA^* \vec{x}(k) - CE^* \vec{d}(k))$$

(8)

where  $A^*$ ,  $B^*$  and  $E^*$  are the discrete forms of the coefficient matrices A, B, and E.

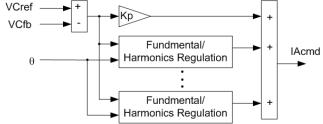

The voltage loop is implemented in synchronous frame with selected harmonics cancellation for both positive and negative sequence components [14]. The simplified voltage regulation block is shown in Fig. 3. The stationary frame voltage error which comes from condenser reference voltage VCref and feedback voltage VCfb is multiplied by the proportional gain (Kp) to create proportional inverter current command which is used to provide fast transient response to the load change.

The load current harmonics are normally slowly varying, so the harmonics regulations for individual selected frequencies (for example, fundamental,  $3^{rd}$ ,  $5^{th}$  and 7th) are implementation in synchronous frame. The advantage of implementing the harmonics regulation in dq frame is that the control variables are dc components which are easy to control and monitor. The output of each harmonics regulators are added together to create the integral portion of inverter current command. Antiwindup technique and the amplitude limiting for each harmonics regulation output should be used to avoid the overflow of the control current command. A feed forward signal proportional to the load current is also added to the command current in order to provide fast dynamic response to the load change.

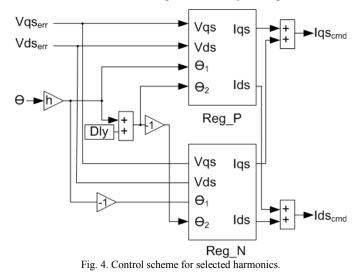

Fig. 4 shows the control scheme where gain h is the order of harmonics. Similar function block for the fundamental and harmonics regulations can be used. Positive sequence regulation and negative sequence regulations are both implemented in synchronous frame with integral (I) controller only as shown in Fig. 5. The stationary frame voltage error is first converted in synchronous frame. Then integral controller is used on the synchronous frame voltage error. After that, the synchronous frame current command is transformed back to stationary frame.

An angle offset corresponding to the time of about one to two PWM cycles should be added to compensate the system delay which is important for the compensation of higher order of harmonics. The main disadvantage of using many harmonics compensators in the control is the computational complexity related to transformation and control for each harmonics. Therefore, a fast processor may be required.

#### Fig. 5. Integral controller of the voltage in synchronous frame.

## III. SIMULATION AND TEST RESULTS

A 125 kW, 480V, 150A inverter based on DSP 320F2812 has been implemented to verify the validation of the proposed control scheme. Fig.6 shows the picture of the 125 kW inverter test setup. The output filter inductor value is 250  $\mu$ H, and capacitor value is 270  $\mu$ F. The switching frequency is 7500 Hz.

Fig. 6. Picture of the 125kW inverter test setup.

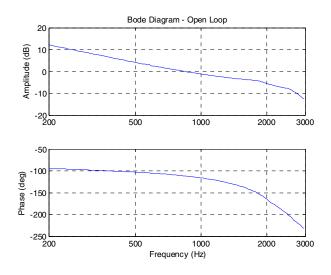

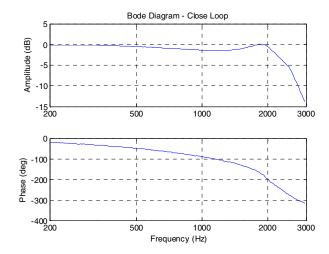

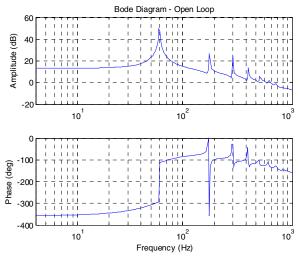

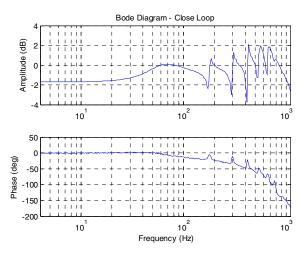

Fig. 7-Fig. 10 show the analyzed current loop and voltage loop transfer functions. The bandwidth of the current loop is

about 2 kHz. The voltage loop has large gains at selected harmonics frequencies.

Fig. 7. Open loop transfer function of the current loop.

Figure 9. Open loop transfer function of the voltage loop.

Fig. 10. Close loop transfer function of the voltage loop.

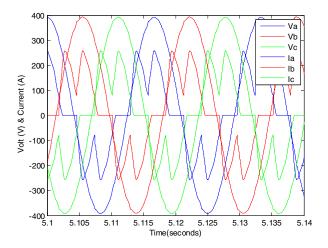

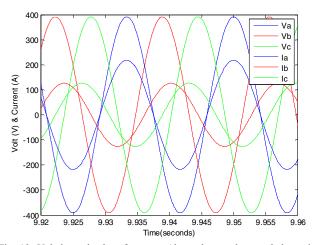

Fig. 11 and Fig. 12 show the simulation results at nonlinear load and unbalanced load conditions. The results show that the proposed controller has very good performance even at nonlinear and unbalanced load conditions.

Fig. 11. Nonlinear load performance (3-single phase rectify with the load of  $3\Omega$ , 4700uF). The voltage THD is 0.77%.

Fig. 12. Unbalance load performance (three-phase voltage unbalance is less than 1%).

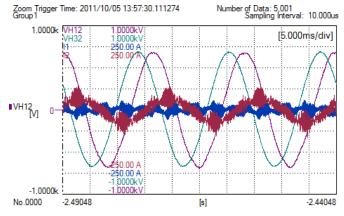

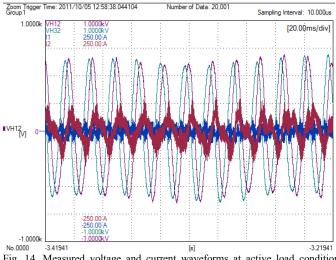

Fig. 13 shows the experimental result at active load condition. The switching frequency of the three-phase active rectifier load is also 7500 Hz. The result shows the voltage output is still stable at active load condition. However, it is worth to mention that because of active load especially with the switching frequency is very close to that of the inverter, sub-harmonics may be created which will make the control unstable as shown in Fig. 14 in which the voltage loop gain has been intentionally made very low at low frequency and also the load feed forward has been reduced.

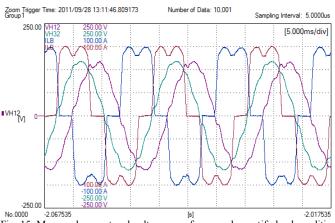

Fig. 15 shows the experimental result at non-linear condition when the output voltage is saturated due to not enough dc bus voltage. Because of the implementation of the anti-windup technique and the amplitude limiting for each harmonics regulation output, when the output voltage is saturated, the output voltage THD will increase but the control can still be stable.

Fig. 13. Measured waveforms at active load condition. (same switching frequency).

Fig. 14. Measured voltage and current waveforms at active load condition when the proportional gain feed forward gain are very low.

Fig. 15. Measured current and voltage waveforms under rectify load condition with output voltage saturation.

### **IV. CONCLUSION**

This paper has described the design of a three-phase fourleg voltage source inverter operating in island mode. An isolation transformer is used to provide isolation and four-wire output. The inner current loop uses high performance DSMC. The voltage loop is implemented in synchronous frame with selected harmonics cancellation for both positive and negative sequence components. The simulation and experimental results of a 125 kW inverter at various operation conditions are presented to verify the validity of the control method.

#### REFERENCES

- IEC 62040-3: Uninterruptible power systems (UPS) Part 3: Method of specifying the performance and test requirements, Mar. 2011.

- [2] Takao Kawabata, Takeshi Miyashita, and Yushin Yamamoto, "Dead Beat Control of Three phase PWM inverter", *IEEE Trans. Power Electronics*, vol., 5 no. 1, Jan. 1990, pp.21-28.

- [3] Osman Kukrer, "Deadbeat control of a three-phase inverter with an output LC filter", *IEEE Trans. Power Electronics*, vol. 11, no. 1, Jan. 1996, pp.16-23.

- [4] A. Kavamura, T.Haneyoshi, and R.G. Hoft, "Deadbeat controlled PWM inverter with parameter estimation using only voltage sensor," IEEE Trans. Power Electron., vol. 3, pp. 118–124, Apr. 1988.

- [5] Takao Kawabata, Takeshi Miyasita, "digital control of three-phase PWM inverter with LC Filter", *IEEE Trans. on Power Electronics*, Jan 1991,pp.62-72.

- [6] S. L. Jung, and Y. Y. Tzou, "Sliding mode control of a closed-loop regulated PWM inverter under large load variations," *IEEE 24<sup>th</sup> annual power electronics specialists conference*, 1993, pp. 616-622.

- [7] S. L. Jung and Y. Y. Tzou, "Discrete feedforward sliding mode control of a PWM inverter for sinusoidal output waveform synthesis," *Proc. IEEE Power Electronics Conference*, 1994, pp. 552–559.

- [8] Fernando Botterón and Humberto Pinheir, "A Three-Phase UPS That Complies With the Standard IEC 62040-3," *IEEE Trans. Industrial Electronics*, vol. 54, no.4, Aug. 2007, pp. 2120-2136.

- [9] J. w. Jung, M. Dai, A. Keyhani, "Optimal Control of Three-Phase PWM Inverter for UPS Systems," 35<sup>th</sup> Annual IEEE Power electronics Specialists Conference, 2004, pp.2054-2059.

- [10] George Weiss, Qing-Chang Zhong, Tim C. Green, and Jun Liang, "H ∞ Repetitive Control of DC-AC Converters in Microgrids," *IEEE Trans. Power Electronics*, vol.19, no.1, Jan. 2004, pp.219-230.

- [11] G. Escobar, A. A. Valdez, J. Leyva-Ramos, and P. Mattavelli, "Repetitive-Based Controller for a UPS Inverter to Compensate Unbalance and Harmonic Distortion," *IEEE Trans. Industry Electronics*, vol. 54, no. 1, Feb. 2007, pp.504-510.

- [12] Peng Xiao, Keith A. Corzine, and Ganesh Kumar Venayagamoorthy, "Multiple Reference Frame-Based Control of Three-Phase PWM Boost Rectifiers under Unbalanced and Distorted Input Conditions", *IEEE Trans. Power Electronics*, vol.23, no.4, July 2008.

- [13] Kyung-Hwan Kim, Nam-Joo Park, and Dong-Seok Hyun, "Advanced Synchronous Reference Frame Controller for Three-phase UPS Powering Unbalanced and Nonlinear Loads", *IEEE 36th Power Electronics Specialists Conference*, 2005. pp.1699 – 1704.

- [14] Paolo Mattavelli, "Synchronous-Frame Harmonic Control for High-Performance AC Power Supplies", *IEEE Trans. Industry Applications*, vol. 37, no. 3, May/June 2001.

- [15] A. Kulka, T. Undeland, S. Vazquez, L.G. Franquelo, "Stationary frame voltage harmonic controller for standalone power generation," 2007 European Conference on Power Electronics and Applications, Sept. 2007, pp.1-10.

- [16] Mohammad N. Marwali, and Ali Keyhani, "Control of Distributed Generation Systems-Part I: Voltages and Currents Control," *IEEE Trans. Power Electronics*, vol. 19, no. 6, Nov. 2004. Pp.1541-1550.

- [17] Min Dai, Mohammad Nanda Marwali, Jin-Woo Jung and Ali Keyhani, "A Three-Phase Four-Wire Inverter Control Technique for a Single Distributed Generation Unit in Island Mode," *IEEE Trans. Power Electronics*, vol.23, no.1, Jan. 2008, pp.322-331.